Baya- AI Enabled SoC Intgration Platform, IP-XACT 1685, UPF, Verilog and VHDL Parsers, Translators & Converters, Datamodel and Re-Writers

Baya - Auto Integration of SoC Components with IP-XACT & Tcl API

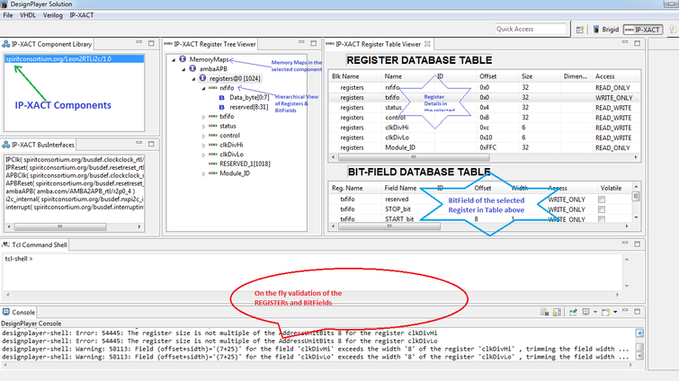

The IEEE IP-XACT 1685 standard enables the use of a unified structure for the meta specification of a design, components, interfaces, documentation, interconnection of components, and Memories & Registers. This structure can be used as the basis of both manual and automatic methodologies. IP-XACT specifies the tight generator interface (TGI) for access to the data in a vendor-independent manner.

|

IP-XACT Domain

|

Capabilities and

Features

|

EDAUtils Tools

|

|

Component

|

Smart GUI to capture VLNV,

ports and parameters from brand new IPs

Import component definition

from Verilog and VHDL

Intuitive GUI to create port

and parameters

GUI create Bus Interfaces

along with logical to physical port mappings

Tcl shell commands for the

above for commandline users

Simple translators to convert

VHDL and Verilog into IP-XACT

Coherency checker between RTL

and IP-XACT models

Equivalence checker between

two revisions of Component XML

IP-XACT Validator

IP-XACT Document Generator

|

IP-XACT

GUI

ipxact-shell

verilog2ipxact

vhdl2ipxact

ipxact2vhdlentity

ipxat2verilog

validateipxact

ipxact2tcl

gendocipxact

ipxactcoherencychecker

|

|

Register & Memories

|

Single sourced GUI to create

Address Block and Memory Map file

Correct by construct

Register, Alternate Register and Bit Field capture

UVM Model generator

C Model generator

IP-XACT Validator

Excel/CSV to IP-XACT Address Block Generator

|

IP-XACT

GUI

ipxact-shell

genregisteruvmmodel

genregistercmodel

validateipxact

ipxact2tcl

xls2ipxact

|

|

Design

|

Create Design from Verilog

Instantiate Components

Insert interface connections

Insert adhoc connections

between port to port

Insert tied values for

unconnected ports

Associate Memory Maps with

the instantiated components to generate C model for the Design(

SoC )

Generate Verilog from IP-XACT Design

|

verilog2ipxact

ipxact2verilog

ipxact-shell

|

|

Bus Definition and

Abstraction Definition

|

|

ipxact-shell

Primitive GUI

Tools

|

|

Miscellaneous Utilities

|

Bunch of commonly used utilities around IP-XACT. Most of these utilities were created based upon different user requests over the period of time.

|

ipxact2verilog - Generate Verilog module from IP-XACT definition

ipxact2vhdlentity - Generate VHDL entity from IP-XACT Component definition

verilog2ipxact - Generates IP-XACT definition from Verilog modules

vhdl2ipxact - Generates IP-XACT definition from VHDL source

ipxactcoherencycheckerverilog - Validates IP-XACT Component definition with Verilog implementation and vice versa

ipxactcoherencycheckervhdl - Validates IP-XACT Component definition with VHDL iEntity and vice versa

validateipxact - IP-XACT Validators, syntaxt and semantic validator of IP-XACT file

compareipxact - Logical comparison of two IP-XACT files

gendocipxact - Generate Word document from IP-XACT definition

ipxact2tlm - Generate Transaction Level Model from IP-XACT Register Definitions

ipxactinterface2svinterface - Generates System Verilog Interface from IP-XACT BusInterface definition

ipxactreg2xlsreg - Generates XLS from IP-XACT file, especially useful for Register management

xls2ipxact - Generates IP-XACT file from XLS file

ipxact2tcl - Generate IP-XACT Tcl comands from an existing file

ipxact-shell - Comprehensive Tcl shell to use all the EDAUtils' capabilities IP-XACT and creation and maintenance of IP-XACT files

|

EDAUtils provides complete IP-XACT solution needed in the design organizations dealing with IP creation or IP integration. It offers an intuitive GUI to build IP-XACT Component defintion by reading the ports and parameters from the RTL, instantiating bus interfaces, intuitively mapping ports and parameters, defining MEMORIES, REGITERS and BITFIELDS and their properties resulting in correct by construction. All the actions in the GUI gets saved into equivalent Tcl commands which can be reused later to update the IP-XACT in batch mode. There is a comprehensive Tcl shell which can be used to create & modify any IP-XACT file upto any extent that anyone may need. Apart from this, there are importers and exporters like verilog2ipxact, vhdl2ipxact, ipxact2verilog and ipxact2vhdl; utility to generate documentation from component. Tool to validate IP-XACT and tool to check consistency between IP-XACT Component and it's Verilog Model. Let's know if you need something which can not be achieved through EDAUtils offerings as listed below table.