The IEEE IP-XACT 1685 standard enables a unified structure for meta specification of designs, components, interfaces, documentation, interconnection, and memories/registers. This structure serves as the basis for both manual and automatic methodologies. IP-XACT specifies the tight generator interface (TGI) for vendor-independent data access.

EDAUtils IP-XACT Offerings

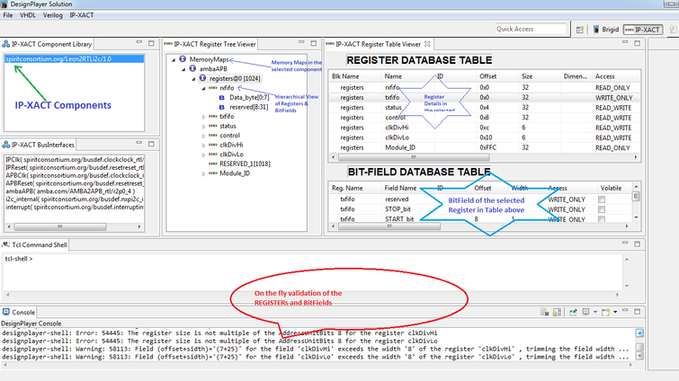

EDAUtils provides complete IP-XACT solutions for design organizations dealing with IP creation or integration. Our intuitive GUI builds IP-XACT Component definitions by reading ports and parameters from RTL, instantiating bus interfaces, intuitively mapping ports/parameters, and defining memories, registers, and bit fields - resulting in correct by construction specifications. All GUI actions generate equivalent Tcl commands for batch mode reuse.

Demo & Tutorials

Capabilities by Domain

| IP-XACT Domain | Capabilities and Features | EDAUtils Tools |

|---|---|---|

| Component |

|

IP-XACT GUI, ipxact-shell, verilog2ipxact, vhdl2ipxact, ipxact2vhdl, ipxact2verilog, validateipxact, gendocipxact, ipxactcoherencychecker |

| Registers & Memories |

|

IP-XACT GUI, ipxact-shell, genregisteruvmmodel, genregistercmodel, validateipxact, ipxact2tcl, xls2ipxact |

| Design |

|

verilog2ipxact, ipxact2verilog, ipxact-shell |

Miscellaneous IP-XACT Utilities

- ipxact2verilog - Generate Verilog module from IP-XACT definition

- ipxact2vhdlentity - Generate VHDL entity from IP-XACT Component

- verilog2ipxact - Generate IP-XACT from Verilog modules

- vhdl2ipxact - Generate IP-XACT from VHDL source

- ipxactcoherencychecker - Validate IP-XACT with Verilog/VHDL implementation

- validateipxact - Syntax and semantic validator

- compareipxact - Logical comparison of two IP-XACT files

- gendocipxact - Generate Word document from IP-XACT

- ipxact2tlm - Generate TLM from IP-XACT Register Definitions

- ipxactinterface2svinterface - Generate SystemVerilog Interface from IP-XACT

- ipxactreg2xlsreg - Generate XLS from IP-XACT for register management

- xls2ipxact - Generate IP-XACT from XLS file

- ipxact2tcl - Generate Tcl commands from existing IP-XACT

- ipxact-shell - Comprehensive Tcl shell for all IP-XACT capabilities